# DC-Correct High Speed Digital Isolators

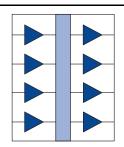

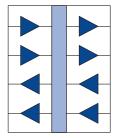

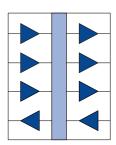

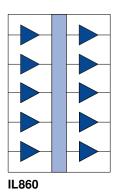

# **Functional Diagrams**

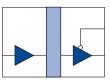

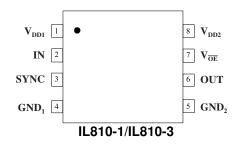

**IL810**

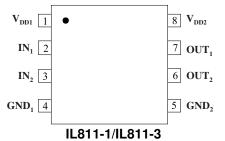

**IL811**

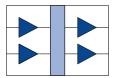

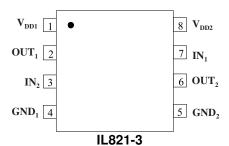

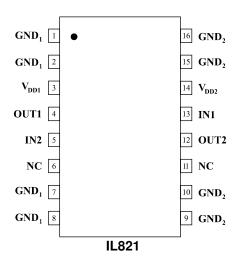

IL821

IL814

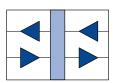

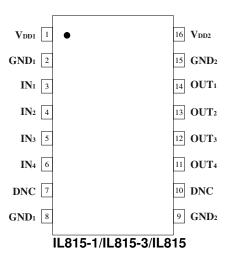

**IL815**

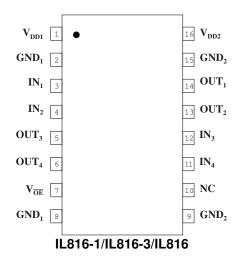

**IL816**

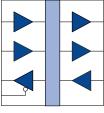

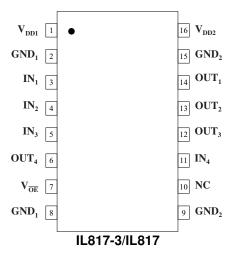

**IL817**

#### **Features**

- DC-correct

- -40 °C to 125 °C operating temperature

- 110 Mbps

- 10 ns propagation delay

- 1.3 mA/channel typical quiescent current

- 50 kV/µs typ.; 30 kV/µs min. common mode transient immunity

- 44000 year barrier life

- 3 V to 5 V power supplies

- Low EMC footprint

- IEC 60747-17 (VDE 0884-17):2021-10 certified; UL 1577 recognized

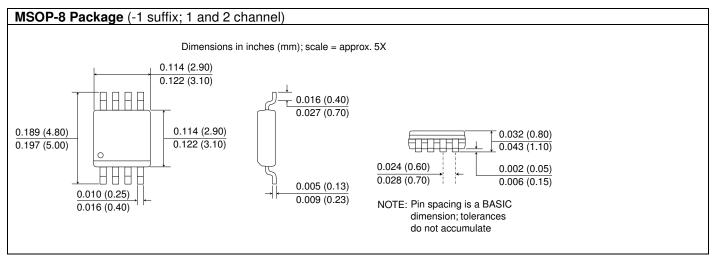

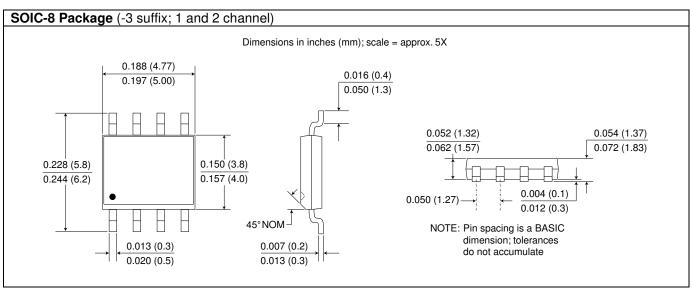

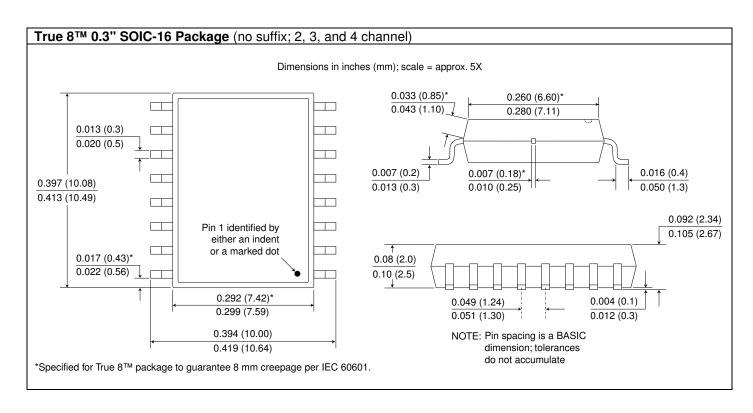

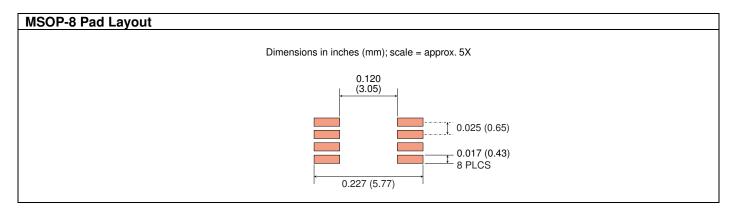

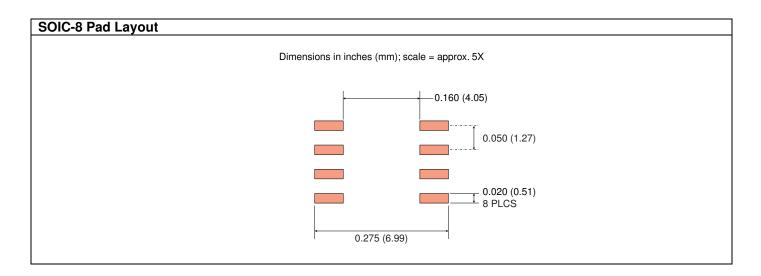

- 8-pin MSOP and SOIC packages for one and two channels

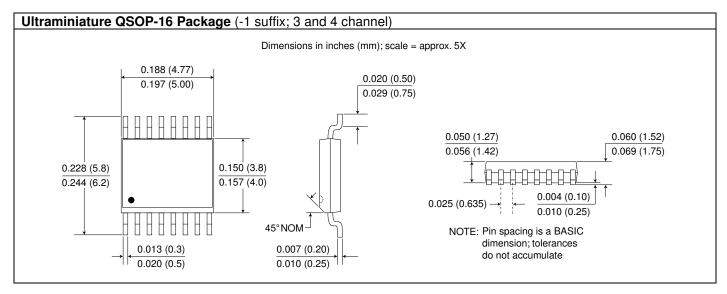

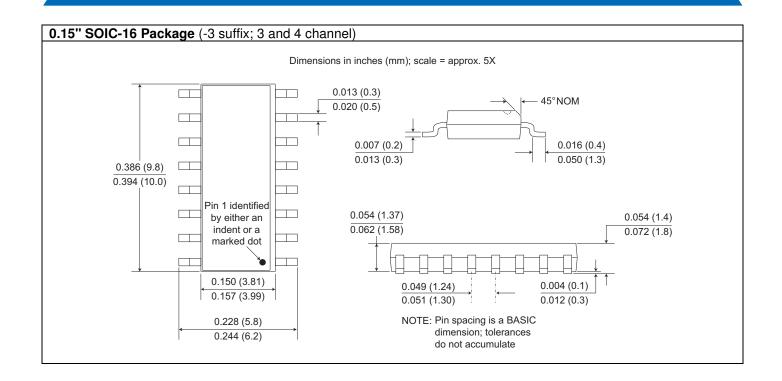

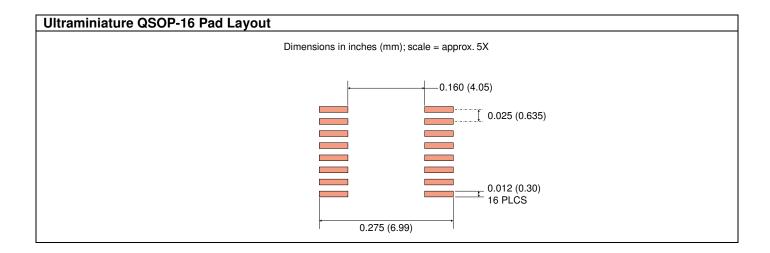

- 16-pin QSOP, 0.15" SOIC, and 0.3" True 8<sup>TM</sup> SOIC for 3, 4, and 5 channels

#### **Applications**

- ADCs and DACs

- Digital Fieldbus

- RS-485 and RS-422

- Multiplexed data transmission

- Data interfaces

- Board-to-board communication

- Digital noise reduction

- Ground loop elimination

- Peripheral interfaces

- Parallel bus

- Logic level shifting

#### Description

IL800-Series isolators are high-speed, high temperature dc-correct isolators. An internal refresh clock ensures the outputs respond to dc states on inputs within a maximum of 9  $\mu s$ .

The devices use NVE's patented\* spintronic Giant Magnetoresistive (GMR) technology.

A unique ceramic/polymer composite barrier provides excellent isolation and virtually unlimited barrier life.

IsoLoop is a registered trademark of NVE Corporation. \*U.S. Patent numbers 5,831,426; 6,300,617 and others.

Absolute Maximum Ratings(1)

| Parameters              | Symbol             | Min. | Тур. | Max.           | Units | Test Conditions |

|-------------------------|--------------------|------|------|----------------|-------|-----------------|

| Storage Temperature     | $T_{S}$            | -55  |      | 150            | °C    |                 |

| Junction Temperature    | $T_{J}$            | -55  |      | 150            | °C    |                 |

| Supply Voltage          | $V_{DD1}, V_{DD2}$ | -0.5 |      | 7              | V     |                 |

| Input Voltage           | $V_{\rm I}$        | -0.5 |      | $V_{DD} + 0.5$ | V     |                 |

| Output Voltage          | $V_{0}$            | -0.5 |      | $V_{DD} + 0.5$ | V     |                 |

| Output Current Drive    | $I_{O}$            |      |      | 10             | mA    |                 |

| Lead Solder Temperature |                    |      |      | 260            | °C    | 10 sec.         |

| ESD                     |                    |      | 2    |                | kV    | HBM             |

**Recommended Operating Conditions**

| Parameters                                       | Symbol                  | Min. | Тур.       | Max.                        | Units | <b>Test Conditions</b> |

|--------------------------------------------------|-------------------------|------|------------|-----------------------------|-------|------------------------|

| Operating Ambient Temperature                    | $T_{A}$                 | -40  |            | 125*                        | °C    |                        |

| Operating Junction Temperature                   | $T_{J}$                 | -40  |            | 125*                        | °C    |                        |

| Supply Voltage                                   | $V_{DD1}, V_{DD2}$      | 3.0  |            | 5.5                         | V     |                        |

| Logic High Input Voltage                         | $V_{IH}$                | 2.4  |            | $V_{\scriptscriptstyle DD}$ | V     |                        |

| Logic Low Input Voltage                          | $V_{\rm IL}$            | 0    |            | 0.8                         | V     |                        |

| Input Signal Rise and Fall Times <sup>(10)</sup> | $t_{\rm IR},t_{\rm IF}$ |      | DC-Correct |                             |       |                        |

<sup>\*</sup>IL860-1 max. operating ambient and junction temperature is 100 °C; all other part types are 125 °C.

#### **Thermal Characteristics**

| Parameter           | Package      | Symbol                                       | Min. | Тур. | Max. | Units | <b>Test Conditions</b> |

|---------------------|--------------|----------------------------------------------|------|------|------|-------|------------------------|

|                     | MSOP8        |                                              |      | 184  |      |       |                        |

| Junction-Ambient    | SOIC8        |                                              |      | 134  |      |       |                        |

| Thermal Resistance  | QSOP16       | $\Theta_{\scriptscriptstyle \mathrm{JA}}$    |      | 100  |      | °C/W  |                        |

| Thermal Resistance  | 0.15" SOIC16 |                                              |      | 82   |      |       |                        |

|                     | 0.3" SOIC16  |                                              |      | 55   |      |       | Per JESD51; 2s2p       |

|                     | MSOP8        |                                              |      | 15   |      |       | board in free air      |

| Junction–Case (Top) | SOIC8        |                                              |      | 10   |      |       |                        |

| Thermal Resistance  | QSOP16       | $\theta_{	ext{JC}}$                          |      | 9    |      | °C/W  |                        |

| Thermal Resistance  | 0.15" SOIC16 |                                              |      | 8    |      |       |                        |

|                     | 0.3" SOIC16  |                                              |      | 12   |      |       |                        |

|                     | MSOP8        |                                              |      |      | 500  |       |                        |

|                     | SOIC8        |                                              |      |      | 675  |       |                        |

| Power Dissipation   | QSOP16       | $\mathbf{P}_{\scriptscriptstyle \mathrm{D}}$ |      |      | 675  | mW    |                        |

|                     | 0.15" SOIC16 |                                              |      |      | 700  |       |                        |

|                     | 0.3" SOIC16  |                                              |      |      | 800  |       |                        |

### **Safety and Approvals**

IEC 60747-17 (VDE 0884-17):2021-10 (Basic Isolation; VDE File Number 5016933-4880-0001):

- Isolation voltage (V<sub>ISO</sub>): 2500 V<sub>RMS</sub>

- Transient overvoltage (V<sub>IOTM</sub>): 4000 V<sub>PK</sub>

- Surge rating 4000 V

- Each part tested at 1590 VPK for 1 second, 5 pC partial discharge limit

- $\bullet$  Samples tested at 4000  $V_{PK}$  for 60 sec.; then 1358  $V_{PK}$  for 10 sec. with 5 pC partial discharge limit

- Working Voltage (V<sub>IORM</sub>; pollution degree 2):

| Package                               | Part No.<br>Suffix | Working<br>Voltage               |

|---------------------------------------|--------------------|----------------------------------|

| MSOP8                                 | -1                 | $800  \mathrm{V}_{\mathrm{RMS}}$ |

| SOIC8                                 | -3                 | $700  \mathrm{V}_{\mathrm{RMS}}$ |

| QSOP16                                | -1                 | 600 V <sub>RMS</sub>             |

| Narrow-body SOIC16                    | -3                 | $700  \mathrm{V}_{\mathrm{RMS}}$ |

| Wide-body SOIC16/True 8 <sup>TM</sup> | None               | 600 V <sub>RMS</sub>             |

| Safety-Limiting Values                           | Symbol | Value | Units |

|--------------------------------------------------|--------|-------|-------|

| Safety rating ambient temperature                | $T_S$  | 180   | °C    |

| Safety rating power (180°C)                      | Ps     | 270   | mW    |

| Supply current safety rating (total of supplies) | Is     | 54    | mA    |

UL 1577 (Component Recognition Program File Number E207481)

- 2500 V rating for all types other than MSOP

- Each part other than MSOP tested at 3000 V<sub>RMS</sub> (4240 V<sub>PK</sub>) for 1 second; each lot sample tested at 2500 V<sub>RMS</sub> (3530 V<sub>PK</sub>) for 1 minute

- MSOP rating 1000 V; tested at 1200 V<sub>RMS</sub> (1768 V<sub>PK</sub>) for 1 second; each lot sample tested at 1500 V<sub>RMS</sub> (2121 V<sub>PK</sub>) for 1 minute

#### **Soldering Profile**

Per JEDEC J-STD-020C, MSL 1

## IL810-1/IL810-3 Pin Connections

|   | 1/12010            |                                                                                                      |

|---|--------------------|------------------------------------------------------------------------------------------------------|

| 1 | $V_{\mathrm{DD1}}$ | Supply voltage                                                                                       |

| 2 | IN                 | Data in                                                                                              |

| 3 | SYNC               | Internal refresh clock disable (normally enabled and internally held low with $10 \text{ k}\Omega$ ) |

| 4 | GND <sub>1</sub>   | Ground return for V <sub>DD1</sub>                                                                   |

| 5 | GND <sub>2</sub>   | Ground return for V <sub>DD2</sub>                                                                   |

| 6 | OUT                | Data out                                                                                             |

| 7 | Voe                | Output enable (internally held low with $100 \text{ k}\Omega$ )                                      |

| 8 | $V_{\mathrm{DD2}}$ | Supply voltage                                                                                       |

## IL811-1/IL811-3 Pin Connections

| 1 | $V_{\mathrm{DD1}}$ | Supply voltage                     |

|---|--------------------|------------------------------------|

| 2 | $IN_1$             | Data in, channel 1                 |

| 3 | $IN_2$             | Data in, channel 2                 |

| 4 | GND <sub>1</sub>   | Ground return for V <sub>DD1</sub> |

| 5 | $GND_2$            | Ground return for V <sub>DD2</sub> |

| 6 | OUT <sub>2</sub>   | Data out, channel 2                |

| 7 | OUT <sub>1</sub>   | Data out, channel 1                |

| 8 | $V_{\mathrm{DD2}}$ | Supply voltage                     |

#### **IL821-3 Pin Connections**

| 1 | $V_{DD1}$          | Supply voltage                     |

|---|--------------------|------------------------------------|

| 2 | OUT <sub>1</sub>   | Data out, channel 1                |

| 3 | $IN_2$             | Data in, channel 2                 |

| 4 | GND <sub>1</sub>   | Ground return for V <sub>DD1</sub> |

| 5 | GND <sub>2</sub>   | Ground return for V <sub>DD2</sub> |

| 6 | OUT <sub>2</sub>   | Data out, channel 2                |

| 7 | $IN_1$             | Data in, channel 1                 |

| 8 | $V_{\mathrm{DD2}}$ | Supply voltage                     |

## IL814-1/IL814-3/IL814 Pin Connections

|    | 1712011            | On Edit in Connections                            |

|----|--------------------|---------------------------------------------------|

| 1  | $V_{\mathrm{DD1}}$ | Supply voltage 1                                  |

| 2  | $GND_1$            | Ground return for V <sub>DD1</sub>                |

|    | GNDI               | (pin 2 internally connected to pin 8)             |

| 3  | $IN_1$             | Data in, channel 1                                |

| 4  | IN <sub>2</sub>    | Data in, channel 2                                |

| 5  | OUT <sub>3</sub>   | Data out, channel 3                               |

| 6  | NC                 | No connection                                     |

| 7  |                    | Output enable, channel 3                          |

| /  | Voe                | (internally held low with $100 \text{ k}\Omega$ ) |

| 8  | GND <sub>1</sub>   | Ground return for V <sub>DD1</sub>                |

| 0  |                    | (pin 8 internally connected to pin 2)             |

| 9  | GND <sub>2</sub>   | Ground return for V <sub>DD2</sub>                |

| 9  |                    | (pin 9 internally connected to pin 15)            |

| 10 | NC                 | No connection                                     |

| 11 | NC                 | No connection                                     |

| 12 | $IN_3$             | Data in, channel 3                                |

| 13 | OUT <sub>2</sub>   | Data out, channel 2                               |

| 14 | OUT <sub>1</sub>   | Data out, channel 1                               |

| 15 | CND                | Ground return for V <sub>DD2</sub>                |

| 15 | GND <sub>2</sub>   | (pin 15 internally connected to pin 9)            |

| 16 | $V_{\mathrm{DD2}}$ | Supply voltage                                    |

| $\mathbf{V_{DD1}}$ 1     | •                          | 16 | $\mathbf{V}_{\mathrm{DD2}}$ |

|--------------------------|----------------------------|----|-----------------------------|

| $GND_1$ 2                |                            | 15 | GND <sub>2</sub>            |

| <b>IN</b> <sub>1</sub> 3 |                            | 14 | OUT <sub>1</sub>            |

| IN <sub>2</sub> 4        |                            | 13 | OUT <sub>2</sub>            |

| OUT <sub>3</sub> 5       |                            | 12 | IN <sub>3</sub>             |

| NC 6                     |                            | 11 | NC                          |

| $V_{\overline{OE}}$ 7    |                            | 10 | NC                          |

| GND <sub>1</sub> 8       |                            | 9  | GND <sub>2</sub>            |

| ı                        | <br>  814-1/   814-3/   81 | 4  |                             |

## IL815-1/IL815-3/IL815 Pin Connections

| 1  | $V_{\mathrm{DD1}}$ | Supply voltage                         |

|----|--------------------|----------------------------------------|

| 2  | GND <sub>1</sub>   | Ground return for V <sub>DD1</sub>     |

|    | GIVDI              | (pin 2 internally connected to pin 8)  |

| 3  | $IN_1$             | Data in, channel 1                     |

| 4  | $IN_2$             | Data in, channel 2                     |

| 5  | IN <sub>3</sub>    | Data in, channel 3                     |

| 6  | $IN_4$             | Data in, channel 4                     |

| 7  | DNC                | Do Not Connect (test pin)              |

| 8  | GND <sub>1</sub>   | Ground return for V <sub>DD1</sub>     |

| 0  |                    | (pin 8 internally connected to pin 2)  |

| 9  | GND <sub>2</sub>   | Ground return for V <sub>DD2</sub>     |

| ,  |                    | (pin 9 internally connected to pin 15) |

| 10 | DNC                | Do Not Connect (test pin)              |

| 11 | OUT <sub>4</sub>   | Data out, channel 4                    |

| 12 | OUT <sub>3</sub>   | Data out, channel 3                    |

| 13 | OUT <sub>2</sub>   | Data out, channel 2                    |

| 14 | OUT <sub>1</sub>   | Data out, channel 1                    |

| 15 | CND                | Ground return for V <sub>DD2</sub>     |

| 13 | GND <sub>2</sub>   | (pin 15 internally connected to pin 9) |

| 16 | $V_{\mathrm{DD2}}$ | Supply voltage                         |

#### IL816-1/IL816-3/IL816 Pin Connections

|    | 1712010             | O/ILOTO I III OOIIIICOLIOIIS           |

|----|---------------------|----------------------------------------|

| 1  | $V_{\mathrm{DD1}}$  | Supply voltage                         |

| 2  | CND                 | Ground return for V <sub>DD1</sub>     |

|    | $GND_1$             | (pin 2 internally connected to pin 8)  |

| 3  | $IN_1$              | Data in, channel 1                     |

| 4  | IN <sub>2</sub>     | Data in, channel 2                     |

| 5  | OUT <sub>3</sub>    | Data out, channel 3                    |

| 6  | OUT <sub>4</sub>    | Data out, channel 4                    |

| 7  |                     | Output enable, channels 3 and 4        |

| /  | $V_{\overline{OE}}$ | (internally held low with 100 kΩ)      |

| 8  | GND <sub>1</sub>    | Ground return for V <sub>DD1</sub>     |

| 0  |                     | (pin 8 internally connected to pin 2)  |

| 9  | GND <sub>2</sub>    | Ground return for V <sub>DD2</sub>     |

| 9  |                     | (pin 9 internally connected to pin 15) |

| 10 | NC                  | No connection                          |

| 11 | IN <sub>4</sub>     | Data in, channel 4                     |

| 12 | IN <sub>3</sub>     | Data in, channel 3                     |

| 13 | OUT <sub>2</sub>    | Data out, channel 2                    |

| 14 | OUT <sub>1</sub>    | Data out, channel 1                    |

| 15 | GND <sub>2</sub>    | Ground return for V <sub>DD2</sub>     |

| 13 | GND <sub>2</sub>    | (pin 15 internally connected to pin 9) |

| 16 | $V_{\mathrm{DD2}}$  | Supply voltage                         |

|    |                     |                                        |

## IL817-3/IL817 Pin Connections

| 1  | $V_{DD1}$                      | Supply voltage                                    |  |  |  |

|----|--------------------------------|---------------------------------------------------|--|--|--|

| 2  | CND                            | Ground return for V <sub>DD1</sub>                |  |  |  |

| 2  | GND <sub>1</sub>               | (pin 2 internally connected to pin 8)             |  |  |  |

| 3  | $IN_1$                         | Data in, channel 1                                |  |  |  |

| 4  | $IN_2$                         | Data in, channel 2                                |  |  |  |

| 5  | IN <sub>3</sub>                | Data in, channel 3                                |  |  |  |

| 6  | OUT <sub>4</sub>               | Data out, channel 4                               |  |  |  |

| 7  |                                | Output enable, channel 4                          |  |  |  |

| /  | $V_{\overline{0}\overline{E}}$ | (internally held low with $100 \text{ k}\Omega$ ) |  |  |  |

| 8  | GND <sub>1</sub>               | Ground return for V <sub>DD1</sub>                |  |  |  |

| 0  |                                | (pin 8 internally connected to pin 2)             |  |  |  |

| 9  | GND <sub>2</sub>               | Ground return for V <sub>DD2</sub>                |  |  |  |

| ,  | OND2                           | (pin 9 internally connected to pin 15)            |  |  |  |

| 10 | NC                             | No connection                                     |  |  |  |

| 11 | IN <sub>4</sub>                | Data in, channel 4                                |  |  |  |

| 12 | OUT <sub>3</sub>               | Data out, channel 3                               |  |  |  |

| 13 | OUT <sub>2</sub>               | Data out, channel 2                               |  |  |  |

| 14 | OUT <sub>1</sub>               | Data out, channel 1                               |  |  |  |

| 15 | CND                            | Ground return for V <sub>DD2</sub>                |  |  |  |

| 13 | $GND_2$                        | (pin 15 internally connected to pin 9)            |  |  |  |

| 16 | $V_{\mathrm{DD2}}$             | Supply voltage                                    |  |  |  |

## **IL821 Pin Connections**

| 1 2 | GND <sub>1</sub> | Ground return for V <sub>DD1</sub> (pins 1, 2, 7, and 8 internally connected) |  |  |  |  |

|-----|------------------|-------------------------------------------------------------------------------|--|--|--|--|

| 3   | $V_{DD1}$        | Supply voltage                                                                |  |  |  |  |

| 4   | OUT <sub>1</sub> | Data out, channel 1                                                           |  |  |  |  |

| 5   | IN <sub>2</sub>  | Data in, channel 2                                                            |  |  |  |  |

| 6   | NC               | No connection                                                                 |  |  |  |  |

| 7   | GND <sub>1</sub> | Ground return for V <sub>DD1</sub>                                            |  |  |  |  |

| 8   | GNDI             | (pins 1, 2, 7, and 8 internally connected)                                    |  |  |  |  |

| 9   | $GND_2$          | Ground return for V <sub>DD2</sub>                                            |  |  |  |  |

| 10  | $OND_2$          | (pins 9, 10, 15, and 16 internally connected)                                 |  |  |  |  |

| 11  | NC               | No connection                                                                 |  |  |  |  |

| 12  | OUT <sub>2</sub> | Data out, channel 2                                                           |  |  |  |  |

| 13  | $IN_1$           | Data in, channel 1                                                            |  |  |  |  |

| 14  | $V_{DD2}$        | Supply voltage                                                                |  |  |  |  |

| 15  | GND <sub>2</sub> | Ground return for V <sub>DD2</sub>                                            |  |  |  |  |

| 16  | GIND2            | (pins 9, 10, 15, and 16 internally connected)                                 |  |  |  |  |

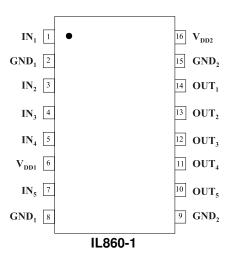

# **IL860-1 Pin Connections**

| 1  | $IN_1$             | Data in, channel 1                     |

|----|--------------------|----------------------------------------|

| 2  | $GND_1$            | Ground return for V <sub>DD1</sub>     |

|    | OND                | (pin 2 internally connected to pin 8)  |

| 3  | $IN_2$             | Data in, channel 2                     |

| 4  | $IN_3$             | Data in, channel 3                     |

| 5  | IN <sub>4</sub>    | Data in, channel 4                     |

| 6  | $V_{\mathrm{DD1}}$ | Supply voltage                         |

| 7  | IN <sub>5</sub>    | Data in, channel 5                     |

| 8  | GND <sub>1</sub>   | Ground return for V <sub>DD1</sub>     |

| 0  | GNDI               | (pin 8 internally connected to pin 2)  |

| 9  | GND <sub>2</sub>   | Ground return for V <sub>DD2</sub>     |

| ,  | OND2               | (pin 9 internally connected to pin 15) |

| 10 | OUT <sub>5</sub>   | Data out, channel 5                    |

| 11 | OUT <sub>4</sub>   | Data out, channel 4                    |

| 12 | OUT <sub>3</sub>   | Data out, channel 3                    |

| 13 | OUT <sub>2</sub>   | Data out, channel 2                    |

| 14 | OUT <sub>1</sub>   | Data out, channel 1                    |

| 15 | GND                | Ground return for V <sub>DD2</sub>     |

| 13 | $GND_2$            | (pin 15 internally connected to pin 9) |

| 16 | $V_{\mathrm{DD2}}$ | Supply voltage                         |

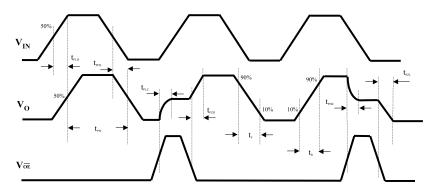

## **Timing Diagrams**

#### Legend

|                    | -                                         |

|--------------------|-------------------------------------------|

| t <sub>PLH</sub>   | Propagation Delay, Low to High            |

| $t_{\mathrm{PHL}}$ | Propagation Delay, High to Low            |

| $t_{\mathrm{PW}}$  | Minimum Pulse Width                       |

| $t_{PLZ}$          | Propagation Delay, Low to High Impedance  |

| $t_{PZH}$          | Propagation Delay, High Impedance to High |

| $t_{\mathrm{PHZ}}$ | Propagation Delay, High to High Impedance |

| $t_{\mathrm{PZL}}$ | Propagation Delay, High Impedance to Low  |

| $t_R$              | Rise Time                                 |

| $t_F$              | Fall Time                                 |

# **Truth Tables**

# **Output Enable**

| $V_{\rm I}$ | $V_{\overline{0}\overline{E}}$ | Vo |

|-------------|--------------------------------|----|

| L           | L                              | L  |

| Н           | L                              | Н  |

| L           | Н                              | Z  |

| Н           | Н                              | Z  |

#### **SYNC**

| SYNC | Internal Refresh Clock |

|------|------------------------|

| 0    | Enabled                |

| 1    | Disabled               |

Note: SYNC should be left open or connected to GND to enable the internal refresh clock, or connected to  $V_{\text{DD}}$  to disable the internal clock.

| 3.3 Volt Electrical Specifications ( $T_{min}$ to $T_{max}$ unless otherwise stated) |                    |                        |                       |      |       |                                     |  |

|--------------------------------------------------------------------------------------|--------------------|------------------------|-----------------------|------|-------|-------------------------------------|--|

| Parameters                                                                           | Symbol             | Min.                   | Тур.                  | Max. | Units | Test Conditions                     |  |

| Input Quiescent Supply Current                                                       |                    |                        |                       |      |       |                                     |  |

| IL810                                                                                |                    |                        | 0.06                  | 0.1  |       |                                     |  |

| IL811                                                                                |                    |                        | 0.09                  | 0.15 |       |                                     |  |

| IL815, IL860                                                                         | $I_{DD1}$          |                        | 0.15                  | 0.25 | mA    |                                     |  |

| IL812, IL814, IL817, IL821                                                           |                    |                        | 1.3                   | 1.8  |       |                                     |  |

| IL816                                                                                |                    |                        | 2.6                   | 3.6  |       |                                     |  |

| Output Quiescent Supply Current                                                      |                    |                        |                       |      |       |                                     |  |

| IL810, IL812, IL821                                                                  |                    |                        | 1.3                   | 1.8  |       |                                     |  |

| IL811, IL814, IL816                                                                  |                    |                        | 2.6                   | 3.6  |       |                                     |  |

| IL815                                                                                | $I_{\mathrm{DD2}}$ |                        | 5.2                   | 7.2  | mA    |                                     |  |

| IL817                                                                                |                    |                        | 3.9                   | 5.4  |       |                                     |  |

| IL860                                                                                |                    |                        | 6.8                   | 9    |       |                                     |  |

| Logic Input Current                                                                  | $I_{\mathrm{I}}$   | -10                    |                       | 10   | μA    |                                     |  |

| Logio High Output Voltago                                                            | Voh                | $V_{DD}$ - 0.1         | $V_{ m DD}$           |      | V     | $I_0 = -20 \mu A, V_I = V_{IH}$     |  |

| Logic High Output Voltage                                                            | V OH               | $0.8 \text{ x V}_{DD}$ | 0.9 x V <sub>DD</sub> |      | V     | $I_0 = -4 \text{ mA}, V_I = V_{IH}$ |  |

| Lacia Law Output Valtage                                                             | V                  |                        | 0                     | 0.1  | V     | $I_0 = 20 \mu A,  V_I = V_{IL}$     |  |

| Logic Low Output Voltage                                                             | $V_{OL}$           | <u>.</u>               | 0.5                   | 0.8  | 7 V   | $I_0 = 4 \text{ mA}, V_I = V_{IL}$  |  |

|                                                                                   | Switching Specifications ( $V_{DD} = 3.3 \text{ V}$ ) |     |     |     |         |                                                                                        |  |

|-----------------------------------------------------------------------------------|-------------------------------------------------------|-----|-----|-----|---------|----------------------------------------------------------------------------------------|--|

| Maximum Data Rate                                                                 |                                                       | 100 | 110 |     | Mbps    | $C_L = 15 \text{ pF}$                                                                  |  |

| Pulse Width <sup>(7)</sup>                                                        | PW                                                    | 10  |     |     | ns      | V <sub>0</sub> 50% points;                                                             |  |

| Propagation Delay Input to Output (High to Low)                                   | t <sub>PHL</sub>                                      |     | 12  | 18  | ns      | $C_L = 15 \text{ pF}$                                                                  |  |

| Propagation Delay Input to Output (Low to High)                                   | tplh                                                  |     | 12  | 18  | ns      | $C_L = 15 \text{ pF}$                                                                  |  |

| Propagation Delay Enable to Output (High to High Impedance)                       | t <sub>PHZ</sub>                                      |     |     | 5   | ns      | $C_L = 15 \text{ pF}$                                                                  |  |

| Propagation Delay Enable to Output (Low to High Impedance)                        | $t_{PLZ}$                                             |     |     | 5   | ns      | $C_L = 15 \text{ pF}$                                                                  |  |

| Propagation Delay Enable to Output (High Impedance to High)                       | tрzн                                                  |     |     | 5   | ns      | $C_L = 15 \text{ pF}$                                                                  |  |

| Propagation Delay Enable to Output (High Impedance to Low)                        | t <sub>PZL</sub>                                      |     |     | 5   | ns      | $C_L = 15 \text{ pF}$                                                                  |  |

| Pulse Width Distortion <sup>(2)</sup>                                             | PWD                                                   |     | 2   | 3   | ns      | $C_L = 15 \text{ pF}$                                                                  |  |

| Propagation Delay Skew <sup>(3)</sup>                                             | tpsk                                                  |     | 4   | 6   | ns      | $C_L = 15 \text{ pF}$                                                                  |  |

| Output Rise Time (10%–90%)                                                        | $t_R$                                                 |     | 2   | 4   | ns      | $C_L = 15 \text{ pF}$                                                                  |  |

| Output Fall Time (10%–90%)                                                        | t <sub>F</sub>                                        |     | 2   | 4   | ns      | $C_L = 15 \text{ pF}$                                                                  |  |

| Common Mode Transient Immunity<br>(Output Logic High or Logic Low) <sup>(4)</sup> | ICM <sub>H</sub> I,ICM <sub>L</sub> I                 | 30  | 50  |     | kV/μs   | $V_{\text{CM}} = 1500 \text{ V}_{\text{DC}}$<br>$t_{\text{TRANSIENT}} = 25 \text{ ns}$ |  |

| Channel-to-Channel Skew                                                           | $t_{\rm CSK}$                                         |     | 2   | 3   | ns      | $C_L = 15 \text{ pF}$                                                                  |  |

| SYNC Internal Clock Off Time <sup>(11)</sup>                                      | t <sub>OFF</sub>                                      |     |     | 5   | ns      |                                                                                        |  |

| Dynamic Power Consumption <sup>(6)</sup>                                          |                                                       |     | 140 | 240 | μA/Mbps | per channel                                                                            |  |

| Magnetic Field Immunity <sup>(8)</sup> (V <sub>DD2</sub> = 3V, 3V <v<sub>DD1&lt;5.5V)</v<sub> |                |  |      |  |     |                |  |

|-----------------------------------------------------------------------------------------------|----------------|--|------|--|-----|----------------|--|

| Power Frequency Magnetic Immunity H <sub>PF</sub> 1500 A/m 50Hz/60Hz                          |                |  |      |  |     |                |  |

| Pulse Magnetic Field Immunity                                                                 | $H_{PM}$       |  | 2000 |  | A/m | $t_p = 8\mu s$ |  |

| Damped Oscillatory Magnetic Field                                                             | Hosc           |  | 2000 |  | A/m | 0.1Hz – 1MHz   |  |

| Cross-axis Immunity Multiplier <sup>(9)</sup>                                                 | K <sub>X</sub> |  | 2.5  |  |     |                |  |

| <b>5 Volt Electrical Specifications</b> (T <sub>min</sub> to T <sub>max</sub> unless otherwise stated) |                    |                     |                       |      |          |                                     |  |  |

|--------------------------------------------------------------------------------------------------------|--------------------|---------------------|-----------------------|------|----------|-------------------------------------|--|--|

| Parameters                                                                                             | Symbol             | Min.                | Typ.                  | Max. | Units    | Test Conditions                     |  |  |

| Input Quiescent Supply Current                                                                         |                    |                     |                       |      |          |                                     |  |  |

| IL810                                                                                                  |                    |                     | 0.1                   | 0.15 | mA       |                                     |  |  |

| IL811                                                                                                  |                    |                     | 0.15                  | 0.25 | mA       |                                     |  |  |

| IL815, IL860                                                                                           | ${ m I}_{ m DD1}$  |                     | 0.25                  | 0.35 | mA       |                                     |  |  |

| IL814, IL817, IL821                                                                                    |                    |                     | 1.8                   | 2.5  | mA       |                                     |  |  |

| IL816                                                                                                  |                    |                     | 3.6                   | 5    | mA       |                                     |  |  |

| Output Quiescent Supply Current                                                                        |                    |                     |                       |      |          |                                     |  |  |

| IL810, IL821                                                                                           |                    |                     | 1.8                   | 2.5  | mA       |                                     |  |  |

| IL811, IL814, IL816                                                                                    |                    |                     | 3.6                   | 5    | mA       |                                     |  |  |

| IL815                                                                                                  | $I_{\mathrm{DD2}}$ |                     | 7.2                   | 10   | mA       |                                     |  |  |

| IL817                                                                                                  |                    |                     | 5.4                   | 7.5  | mA       |                                     |  |  |

| IL860                                                                                                  |                    |                     | 9                     | 12.5 |          |                                     |  |  |

| Logic Input Current                                                                                    | $I_{\rm I}$        | -10                 |                       | 10   | μA       |                                     |  |  |

| Logio High Output Voltago                                                                              | Vov                | $V_{DD}$ - 0.1      | $V_{ m DD}$           |      | V        | $I_{O} = -20 \mu A, V_{I} = V_{IH}$ |  |  |

| Logic High Output Voltage                                                                              | Voh                | $0.8 \times V_{DD}$ | 0.9 x V <sub>DD</sub> |      | V        | $I_O = -4 \text{ mA}, V_I = V_{IH}$ |  |  |

| Lagia Law Output Valtage                                                                               | Vol                |                     | 0                     | 0.1  | V        | $I_O = 20 \mu A,  V_I = V_{IL}$     |  |  |

| Logic Low Output Voltage                                                                               |                    |                     | 0.5                   | 0.8  | <b>v</b> | $I_0 = 4 \text{ mA}, V_I = V_{IL}$  |  |  |

| Switching Specifications ( $V_{DD} = 5.5 \text{ V}$ )                             |                                       |     |     |     |         |                                                                                        |

|-----------------------------------------------------------------------------------|---------------------------------------|-----|-----|-----|---------|----------------------------------------------------------------------------------------|

| Maximum Data Rate                                                                 |                                       | 100 | 110 |     | Mbps    | $C_L = 15 \text{ pF}$                                                                  |

| Pulse Width <sup>(7)</sup>                                                        | PW                                    | 10  |     |     | ns      | Vo 50% points                                                                          |

| Propagation Delay Input to Output (High to Low)                                   | t <sub>PHL</sub>                      |     | 10  | 15  | ns      | $C_L = 15 \text{ pF}$                                                                  |

| Propagation Delay Input to Output (Low to High)                                   | tplh                                  |     | 10  | 15  | ns      | $C_L = 15 \text{ pF}$                                                                  |

| Propagation Delay Enable to Output (High to High Impedance)                       | t <sub>PHZ</sub>                      |     |     | 5   | ns      | $C_L = 15 \text{ pF}$                                                                  |

| Propagation Delay Enable to Output (Low to High Impedance)                        | $t_{PLZ}$                             |     |     | 5   | ns      | $C_L = 15 \text{ pF}$                                                                  |

| Propagation Delay Enable to Output (High Impedance to High)                       | tрzн                                  |     |     | 5   | ns      | $C_L = 15 \text{ pF}$                                                                  |

| Propagation Delay Enable to Output (High Impedance to Low)                        | t <sub>PZL</sub>                      |     |     | 5   | ns      | $C_L = 15 \text{ pF}$                                                                  |

| Pulse Width Distortion <sup>(2)</sup>                                             | PWD                                   |     | 2   | 3   | ns      | $C_L = 15 \text{ pF}$                                                                  |

| Propagation Delay Skew <sup>(3)</sup>                                             | tpsk                                  |     | 4   | 6   | ns      | $C_L = 15 \text{ pF}$                                                                  |

| Output Rise Time (10%–90%)                                                        | $t_R$                                 |     | 1   | 3   | ns      | $C_L = 15 \text{ pF}$                                                                  |

| Output Fall Time (10%–90%)                                                        | $t_{\mathrm{F}}$                      |     | 1   | 3   | ns      | $C_L = 15 \text{ pF}$                                                                  |

| Common Mode Transient Immunity<br>(Output Logic High or Logic Low) <sup>(4)</sup> | ICM <sub>H</sub> I,ICM <sub>L</sub> I | 30  | 50  |     | kV/μs   | $V_{\text{CM}} = 1500 \text{ V}_{\text{DC}}$<br>$t_{\text{TRANSIENT}} = 25 \text{ ns}$ |

| Channel-to-Channel Skew                                                           | $t_{CSK}$                             |     | 3   | 5   | ns      | $C_L = 15 \text{ pF}$                                                                  |

| SYNC Internal Clock Off Time <sup>(11)</sup>                                      | $t_{OFF}$                             |     |     | 5   | ns      |                                                                                        |

| Dynamic Power Consumption <sup>(6)</sup>                                          |                                       |     | 200 | 340 | μA/Mbps | per channel                                                                            |

| Magnetic Field Immunity <sup>(8)</sup> (V <sub>DD2</sub> = 5V, 3V <v<sub>DD1&lt;5.5V)</v<sub> |          |  |       |  |     |                 |  |

|-----------------------------------------------------------------------------------------------|----------|--|-------|--|-----|-----------------|--|

| Power Frequency Magnetic Immunity H <sub>PF</sub> 3,500 A/m 50Hz/60Hz                         |          |  |       |  |     |                 |  |

| Pulse Magnetic Field Immunity                                                                 | $H_{PM}$ |  | 4,500 |  | A/m | $t_p = 8 \mu s$ |  |

| Damped Oscillatory Magnetic Field                                                             | Hosc     |  | 4,500 |  | A/m | 0.1Hz – 1MHz    |  |

| Cross-axis Immunity Multiplier <sup>(9)</sup>                                                 | Kx       |  | 2.5   |  |     |                 |  |

### **Insulation Specifications**

| Parameters                         |                                               | Symbol   | Min.              | Тур.                        | Max. | Units | Test Conditions                                            |                                  |

|------------------------------------|-----------------------------------------------|----------|-------------------|-----------------------------|------|-------|------------------------------------------------------------|----------------------------------|

| Creepage<br>Distance<br>(external) | MSOP<br>QSOP<br>0.15" SOIC (8 or<br>0.3" SOIC | 16 pin)  |                   | 3.0<br>4.03<br>4.03<br>8.03 | 8.3  |       | mm                                                         | Per IEC 60601                    |

| Total Barrier Thickness (internal) |                                               |          | 0.012             | 0.013                       |      | mm    |                                                            |                                  |

| Leakage Current                    |                                               |          |                   | 0.2                         |      | μA    | 240 V <sub>RMS</sub> , 60 Hz                               |                                  |

| Barrier Resistance                 |                                               | $R_{IO}$ |                   | >1014                       |      | Ω     | 500 V                                                      |                                  |

| Barrier Capacitance                |                                               | $C_{10}$ |                   | 4                           |      | pF    | f = 1  MHz                                                 |                                  |

| Comparative Tracking Index         |                                               | CTI      | ≥175              |                             |      | V     | Per IEC 60112                                              |                                  |

|                                    | ge Endurance<br>Barrier Voltage<br>te Life)   | AC<br>DC | $V_{\mathrm{IO}}$ | 1000<br>1500                |      |       | $V_{ m RMS}$ $V_{ m DC}$                                   | At maximum operating temperature |

| Barrier Life                       |                                               |          |                   | 44000                       |      | Years | 100°C, 1000 V <sub>RMS</sub> , 60%<br>CL activation energy |                                  |

#### **Thermal Characteristics**

| Parameter                                 | Symbol                                                        | Min.              | Тур. | Max.                          | Units                            | Test Conditions |                      |

|-------------------------------------------|---------------------------------------------------------------|-------------------|------|-------------------------------|----------------------------------|-----------------|----------------------|

| Junction-Ambient<br>Thermal Resistance    | MSOP8<br>0.15" SOIC8<br>QSOP16<br>0.15" SOIC16<br>0.3" SOIC16 | $\theta_{ m JA}$  |      | 184<br>134<br>100<br>82<br>67 |                                  |                 | Double-sided PCB in  |

| Junction–Case (Top)<br>Thermal Resistance | MSOP8<br>0.15" SOIC8<br>QSOP16<br>0.15" SOIC16<br>0.3" SOIC16 | $	heta_{ m JC}$   |      | 15<br>10<br>9<br>8<br>12      |                                  | °C/W            | free air             |

| Junction–Ambient<br>Thermal Resistance    | - 0.3" SOIC                                                   | $\theta_{\rm JA}$ |      | 46                            |                                  |                 | 2s2p PCB in free air |

| Junction–Case (Top)<br>Thermal Resistance |                                                               | $\theta_{\rm JC}$ |      | 9                             |                                  |                 | per JESD51           |

| Power Dissipation                         | MSOP8<br>0.15" SOIC8<br>QSOP16<br>0.15" SOIC16<br>0.3" SOIC16 | $P_{D}$           |      |                               | 500<br>675<br>675<br>700<br>1500 | mW              |                      |

#### Notes

- 1. Absolute maximum means the device will not be damaged if operated under these conditions. It does not guarantee performance.

- 2. PWD is defined as |tphl tplh. %PWD is equal to PWD divided by pulse width.

- 3. t<sub>PSK</sub> is the magnitude of the worst-case difference in t<sub>PHL</sub> and/or t<sub>PLH</sub> between devices at 25°C.

- 4.  $CM_H$  is the maximum common mode voltage slew rate that can be sustained while maintaining  $V_0 > 0.8 \ V_{DD2}$ .  $CM_L$  is the maximum common mode input voltage that can be sustained while maintaining  $V_0 < 0.8 \ V$ . The common mode voltage slew rates apply to both rising and falling common mode voltage edges.

- 5. Device is considered a two-terminal device: pins on each side of the package are shorted.

- 6. Dynamic power consumption is calculated per channel and is supplied by the channel's input side power supply.

- 7. Minimum pulse width is the minimum value at which specified PWD is guaranteed.

- 8. The relevant test and measurement methods are given in the Electromagnetic Compatibility section on p. 12.

- 9. External magnetic field immunity is improved by this factor if the field direction is "end-to-end" rather than to "pin-to-pin" (see diagram on p. 12).

- 10. If internal clock is used, devices will respond to DC states on inputs within a maximum of  $9 \mu s$ . Outputs may oscillate if the SYNC input slew rate is less than 1 V/ms.

- 11. toff is the maximum time for the internal refresh clock to shut down.

### **Application Information**

### **Electrostatic Discharge Sensitivity**

This product has been tested for electrostatic sensitivity to the limits stated in the specifications. However, NVE recommends that all integrated circuits be handled with appropriate care to avoid damage. Damage caused by inappropriate handling or storage could range from performance degradation to complete failure.

### **Electromagnetic Compatibility**

IsoLoop Isolators have the lowest EMC footprint of any isolation technology. IsoLoop Isolators' Wheatstone bridge configuration and differential magnetic field signaling ensure excellent EMC performance against all relevant standards.

Additionally, on the IL810, the internal clock can be disabled for even better EMC performance.

These isolators are fully compliant with IEC 61000-6-1 and IEC 61000-6-2 standards for immunity, and IEC 61000-6-3, IEC 61000-6-4, CISPR, and FCC Class A standards for emissions. Immunity to external magnetic fields is even higher if the field direction is "end-to-end" rather than to "pin-to-pin" as shown in the diagram below:

Cross-axis Field Direction

#### **Power Supply Decoupling**

Both power supplies should be decoupled with 0.1  $\mu F$  typical (0.047  $\mu F$  minimum) capacitors as close as possible to the  $V_{DD}$  pins.

#### **Maintaining Creepage**

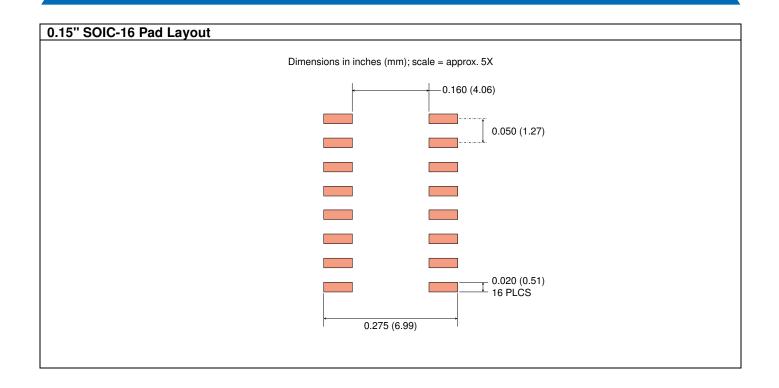

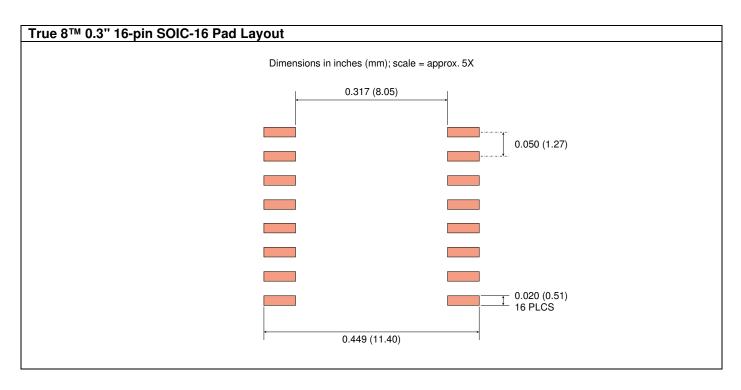

Creepage distances are often critical in isolated circuits. In addition to meeting JEDEC standards, NVE isolator packages have unique creepage specifications. Standard pad libraries often extend under the package, compromising creepage and clearance. Similarly, ground planes, if used, should be spaced to avoid compromising clearance. Package drawings and recommended pad layouts are included in this datasheet.

### **Dynamic Power Consumption**

IsoLoop Isolators achieve their low power consumption from the way they transmit data across the isolation barrier. A magnetic field is created around the GMR Wheatstone bridge by detecting the edge transitions of the input logic signal and converting them to narrow current pulses. Depending on the direction of the magnetic field, the bridge causes the output comparator to switch following the input logic signal. Since the current pulses are narrow, about 2.5 ns, the power consumption is independent of mark-to-space ratio and solely dependent on frequency. This has obvious advantages over optocouplers, which have power consumption heavily dependent on mark-to-space ratio.

#### DC Correctness, EMC, and the SYNC Function

NVE digital isolators have the lowest EMC noise signature of any high-speed digital isolator on the market today because of the dc nature of the GMR sensors used. It is perhaps fair to include opto-couplers in that dc category too, but their limited parametric performance, physically large size, and wear-out problems effectively limit side by side comparisons between NVE's isolators and isolators coupled with RF, matched capacitors, or transformers.

IL800-Series isolators have an internal refresh clock which ensure the synchronization of input and output within 9  $\mu s$  of the supply passing the 1.5 V threshold. The IL810 allows external control of the refresh clock through the SYNC pin thereby further lowering the EMC footprint. This can be advantageous in applications such as hi-fi, motor control and power conversion.

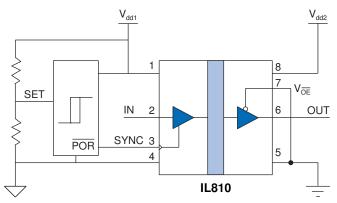

The isolators can be used with Power on Reset (POR) circuits common in microcontroller applications, as the means of ensuring the output of the device is in the same state as the input a short time after power up. Figure 1 shows a practical Power on Reset circuit:

Fig. 1. Typical Power-On Reset Circuit for IL810

After POR, the SYNC line goes high, the internal clock is disabled, and the EMC signature is optimized. Decoupling capacitors are omitted for clarity.

www.nve.com

# **Illustrative Applications**

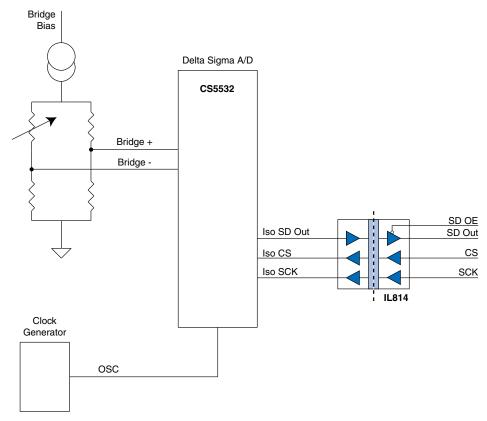

#### Isolated A/D Converter

A delta-sigma A-D converter interfaced with the three-channel IL814. Multiple channels can easily be combined using the IL814's output enable function.

www.nve.com

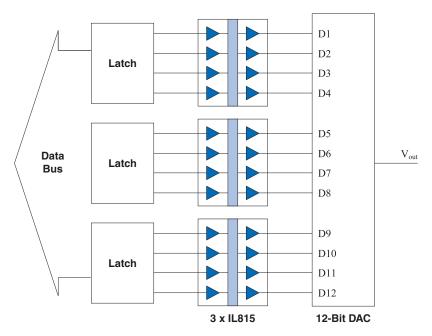

## 12-Bit D/A Converter Isolation

The IL815 four-channel isolator is ideally suited for parallel bus isolation. The circuit above uses three IL815s to isolate a 12-bit DAC.

### **Package Drawings**

www.nve.com

## **Recommended Pad Layouts**

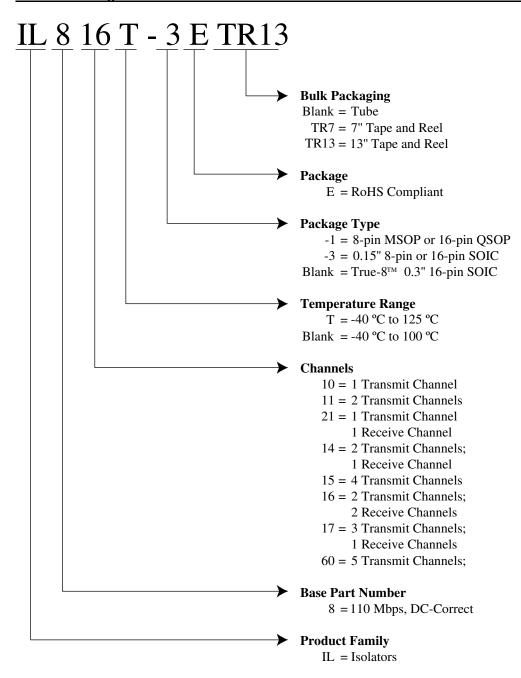

## **Part Numbering**

# **Available Parts**

| Available<br>Parts | Transmit Channels | Receive<br>Channels | Package             | Max.<br>Temperature |

|--------------------|-------------------|---------------------|---------------------|---------------------|

| IL810T-1E          | 1                 | 0                   | MSOP-8              | 125 ℃               |

| IL810T-3E          | 1                 | 0                   | SOIC-8              | 125 ℃               |

| IL811T-1E          | 2                 | 0                   | MSOP-8              | 125 ℃               |

| IL811T-3E          | 2                 | 0                   | SOIC-8              | 125 ℃               |

| IL814T-1E          | 2                 | 1                   | QSOP-16             | 125 ℃               |

| IL814T-3E          | 2                 | 1                   | 0.15" SOIC-16       | 125 ℃               |

| IL814TE            | 2                 | 1                   | True 8 0.3" SOIC-16 | 125 ℃               |

| IL815T-1E          | 4                 | 0                   | QSOP-16             | 125 ℃               |

| IL815T-3E          | 4                 | 0                   | 0.15" SOIC-16       | 125 ℃               |

| IL815TE            | 4                 | 0                   | True 8 0.3" SOIC-16 | 125 ℃               |

| IL816T-1E          | 2                 | 2                   | QSOP-16             | 125 °C              |

| IL816T-3E          | 2                 | 2                   | 0.15" SOIC-16       | 125 ℃               |

| IL816TE            | 2                 | 2                   | True 8 0.3" SOIC-16 | 125 ℃               |

| IL817T-3E          | 3                 | 1                   | 0.15" SOIC-16       | 125 ℃               |

| IL817TE            | 3                 | 1                   | True 8 0.3" SOIC-16 | 125 ℃               |

| IL821T-3E          | 1                 | 1                   | SOIC-8              | 125 ℃               |

| IL821TE            | 1                 | 1                   | True 8 0.3" SOIC-16 | 125 ℃               |

| IL860-1E           | 5                 | 0                   | QSOP-16             | 100 °C              |

#### IBS-DS-001-IL800-M Change: October 2022 • Upgraded to VDE 0884-17 (p. 3). • Increased Working Voltage ratings based on latest VDE testing (p. 3). • Changed IL815 pins 7 and 10 from "NC" to "DNC" to clarify they should not be connected (p. 5). IBS-DS-001-IL800-L Changes: September 2021 • Added five-channel IL860-1. • Upgrade from VDE V 0884-10 to VDE V 0884-11 / IEC 60747-17. IBS-DS-001-IL800-K Changes: • Eliminated IL815 "SYNC" and "OE" functions on lot numbers >201900. April 2020 • Updated EMC standards. • Revised thermal characteristics (p. 11). IBS-DS-001-IL800-J Changes: March 2018 • VDE V 0884-10 (VDE V 0884-11 pending). • MSOP added to UL 1577. • Updated IL810, IL811, and IL815 input quiescent supply current values. SB-DS-001-IL800-I Changes: August 2017 • Corrected order of package type and temperature range suffixes in chart on p. 19. • Deleted obsolete fax number. ISB-DS-001-IL800-H Changes: March 2017 • Corrected 8-pin SOIC package outline dimensions. • Removed minimum Magnetic Field Immunity specification. ISB-DS-001-IL800-G Change: November 2016 • Updated IEC 60747-5-5 (VDE 0884) certification to VDE V 0884-10. ISB-DS-001-IL800-F Changes: June 2014 • Added IL814T-1, IL815T-1, and IL816T-1 QSOP versions. • Dropped IL812 configuration in favor of IL821 two-channel bidirectional configuration. • Updated thermal characteristics. • Added recommended pad layouts. ISB-DS-001-IL800-E Changes: November 2013 • Added IL821TE part type (16-pin True8 wide-body package). • Added output enables to IL816 and IL817. • Clarified pinouts for different package types. • IEC 60747-5-5 (VDE 0884) certification. • Upgraded from MSL 2 to MSL 1.

ISB-DS-001-IL800-D August 2013

### Changes:

• Tighter quiescent current specifications.

• Added IL817 part types.

ISB-DS-001-IL800-C **July 2013**

Changes:

• Added IL812-3 and IL821-3 part types (8-pin SOIC packages).

#### **Datasheet Limitations**

The information and data provided in datasheets shall define the specification of the product as agreed between NVE and its customer, unless NVE and customer have explicitly agreed otherwise in writing. All specifications are based on NVE test protocols. In no event however, shall an agreement be valid in which the NVE product is deemed to offer functions and qualities beyond those described in the datasheet.

#### **Limited Warranty and Liability**

Information in this document is believed to be accurate and reliable. However, NVE does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

In no event shall NVE be liable for any indirect, incidental, punitive, special or consequential damages (including, without limitation, lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

#### **Right to Make Changes**

NVE reserves the right to make changes to information published in this document including, without limitation, specifications and product descriptions at any time and without notice. This document supersedes and replaces all information supplied prior to its publication.

#### Use in Life-Critical or Safety-Critical Applications

Unless NVE and a customer explicitly agree otherwise in writing, NVE products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical devices or equipment. NVE accepts no liability for inclusion or use of NVE products in such applications and such inclusion or use is at the customer's own risk. Should the customer use NVE products for such application whether authorized by NVE or not, the customer shall indemnify and hold NVE harmless against all claims and damages.

#### **Applications**

Applications described in this datasheet are illustrative only. NVE makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NVE products, and NVE accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NVE product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third-party customers. Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NVE does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third-party customers. The customer is responsible for all necessary testing for the customer's applications and products using NVE products in order to avoid a default of the applications and the products or of the application or use by customer's third-party customers. NVE accepts no liability in this respect.

#### **Limiting Values**

Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the recommended operating conditions of the datasheet is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

#### **Terms and Conditions of Sale**

In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NVE hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NVE products by customer.

#### No Offer to Sell or License

Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

#### **Export Control**

This document as well as the items described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.

#### **Automotive Qualified Products**

Unless the datasheet expressly states that a specific NVE product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NVE accepts no liability for inclusion or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NVE's warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NVE's specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NVE for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NVE's standard warranty and NVE's product specifications.

An ISO 9001 Certified Company

**NVE Corporation** 11409 Valley View Road Eden Prairie, MN 55344-3617 USA Telephone: (952) 829-9217

www.nve.com

e-mail: iso-info@nve.com

**©NVE** Corporation

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

ISB-DS-001-IL800T-M

October 2022