#### GMR ISOLATORS

By John Myers and Ty Fayfield

#### A New Type of Device

Advanced thin film magnetic materials are being monolithically combined with silicon integrated circuits to provide a family of high performance, integrated galvanic isolation products. These devices have been demonstrated at Nonvolatile Electronics, Inc. (NVE) and are continuing to be developed under an award granted by the National Institute of Standards and Technology (NIST) Advanced Technology Program (ATP). Historically, the galvanic isolation function has been provided by bulky and/or slow discrete components. This has limited the level of integration and performance which can be attained in systems that require both isolation and active circuitry. The new NVE technology will change this.

#### The Need for Galvanic Isolation

Spatial separation between nodes in an electrical or communications network often results in different nodes on the network having different ground domains. The potential difference between these grounds can be ac or dc and be combined with various noise components. Grounds that are connected together by the cable logic ground or shielding can result in a ground loop such that unwanted current flows in the cable. These ground-loop currents can have several negative effects on the network, which include degradation of data signals on the cable, excessive EMI from the cable, ground currents high enough to damage components in the system, and if the potential difference is large enough, a personal shock hazard.

To eliminate these problems, interfaces which must communicate between circuits or nodes in different ground domains should be galvanically isolated. Galvanic isolation provides a means of seamlessly passing signaling information while isolating ground potential differences and common mode transient events. Besides being a good design practice, isolation components are often mandated in industry standard specifications for applications such as data bus communications where two separate systems interface through common copper connections. Other examples include modems, local area and industrial network interfaces (including network hubs, routers and switches), telephones, switched mode power supplies, printers, and fax machines.

## Today's Approach to Galvanic Isolation

Existing isolation technologies are stable and mature. However, while most components in communications system are rapidly evolving and miniaturizing, the isolation technology has not kept pace. Historically, the isolated signal interface function has required a

combination of discrete passive isolation devices and mixed signal integrated circuits. Existing isolators are based on transformer, optical or capacitive coupling. Their manufacture requires a combination of hand labor, complicated hybrid assembly and/or complex packaging schemes. They cannot be easily integrated with silicon circuitry or other isolation devices. In addition, they all have significant performance drawbacks that present a bottleneck in the quest for faster communications speeds and higher levels of device integration.

## A New Approach to Isolation

To address these shortcomings, NVE is developing a family of devices based on simple isolation building blocks. NVEs patented technology, originally developed with funding from NASA, uniquely integrates Giant Magneto Resistive (GMR) materials, micro coils and integrated circuits into a single silicon-based structure, to produce tiny components that isolate one circuit from another. Single or multiple GMR isolator structures may be monolithically combined with advanced silicon circuit functionality to yield compact, galvanically isolated versions of standard electronic components. Examples include isolated buffers, network interfaces, analog to digital converters and linear amplifiers.

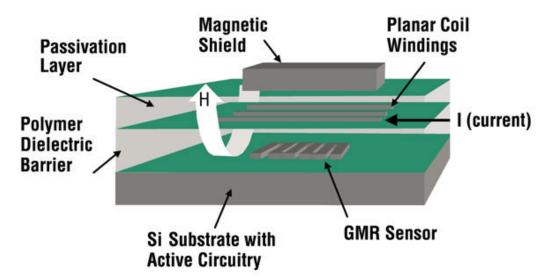

The basic operating principle of the GMR isolator (Figure 1) is discussed below. Resistive planar coil windings are driven by the input current signal to be isolated. A magnetic field, proportional to this input current signal, is generated beneath the coil winding. The resulting magnetic field is sensed across a thick polymer dielectric film by a GMR resistor structure. The dielectric barrier provides high voltage hold-off capability. [The GMR resistors are sensitive to magnetic fields in the plane to the substrate. This enables a more compact integration scheme than would be possible with a Hall sensor, for example, that measures fields perpendicular to the substrate.] The sensed magnetic field is amplified and conditioned with integrated electronic circuits to reproduce an isolated replica of the input signal. Ground potential variations, on the other hand, are common to both sides of the input windings so they do not generate a net current in the coil. Therefore, no magnetic field results and these variations are not sensed by the GMR structures. In this way, the signal is transparently passed from the input to the output circuits while ground potential variations are rejected to achieve true galvanic isolation.

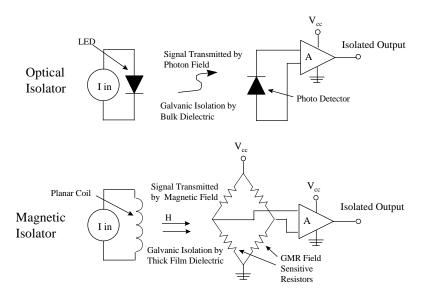

In practice, the device is implemented with some additional improvements. For example, a highly permeable magnetic shield may be placed over the windings (shown in Figure 1) to simultaneously increase the signal magnetic field generated by the coil and to shield the sense element from ambient magnetic fields. In addition, a GMR resistor bridge may be used in place of a single resistor as the sense element. This improves almost all performance parameters including common mode signal rejection and temperature stability. A functional analogy is drawn between the GMR isolator and a conventional optical isolator in figure 2.

Figure 1. GMR Galvanic Signal Isolator Concept

Figure 2. Analogy between GMR isolator and conventional opto-isolator

## **GMR** Isolator Performance Advantages

As mentioned earlier, most existing galvanic isolation is done with either discrete optical isolators or isolation transformers. Optical isolators effectively transmit and isolate signals with frequency components from dc up to some cutoff value. This value, typically less than 10MHz, is too low for many applications. To serve these high frequency applications, isolation transformers must be used. However, transformers cannot pass low frequency or dc signals.

The GMR isolator is functionally analogous to an optical isolator as shown in Figure 2. Like the optical isolator, the GMR version is a unidirectional signal isolator and provides bandwidth down to dc level. In addition, the GMR isolator offers the high frequency performance advantages of the isolation transformer; the GMR device covers nearly the entire bandwidth spanned by these two conventional isolator components in one device. Furthermore, the GMR isolator can be monolithically integrated with silicon circuitry in single or multi-channel implementations.

The present GMR isolators switch between 10 and 100 times faster than the optical isolators (200 MHz), provide nearly 4000 volts of galvanic isolation, and requires less than 1mm<sup>2</sup> of silicon per isolator channel. However, this is not the limit because the GMR material can be switched in less than one nanosecond. Therefore, the bottleneck in frequency performance results from the associated silicon electronics, not the GMR/coil structure. This implies that frequency performance of the isolator device will continuously increase as integrated circuits scale and become faster with each successive improvement in silicon technology.

## Horizontal and Vertical Integration

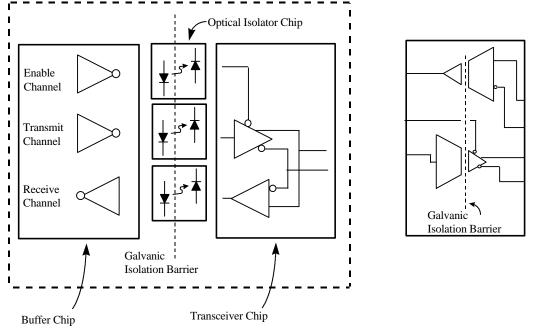

NVEs new approach will use proven integrated circuit manufacturing processes to mass produce isolators at a fraction of the cost and size of existing technologies. In contrast to current solutions, this new technology becomes more cost effective as additional silicon functions are added and as the number of isolation channels is increased. This ability to add the isolation function at the die level allows both horizontal and vertical integration. An isolated interface schematic which demonstrates how GMR integration can leverage both types of integration is shown below in Figure 3. These concepts will be discussed in more detail in the following paragraphs. Bus Transceiver Interface Implemented with Optical Isolators and Separate Silicon Circuitry: Five Packaged Components Bus Transceiver Interface Implemented with GMR Isolators and Monolithic Integrated Circuits: Single Packaged Component

Figure 3: Example of Combined Horizontal and Vertical Integration

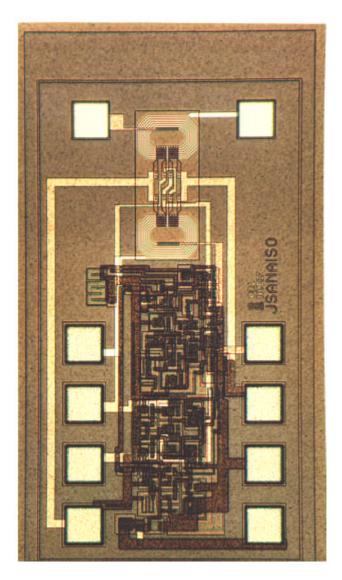

**Horizontal integration** leverage results from the combination of the isolation function and other circuits to make integrated isolated versions of products. These products carry a very a small cost increment and no or little space increment compared to the nonisolated version of the circuit. Examples would be isolated A/D converters, isolation amplifiers, isolated current sensors or an isolated transceiver. It is envisioned that the isolator structure and associated fabrication process module could be made available to designers and fab facilities so that cut and paste'isolated interfaces could be added to almost any circuit needing this feature. This will reduce circuit board component counts, reduce overall circuit board size, lower costs and increase interface speeds. An example of horizontal integration is shown in the photomicrograph of an isolated linear amplifier (Figure 4).

## Figure 4: Photomicrograph of Isolated Linear Amplifier

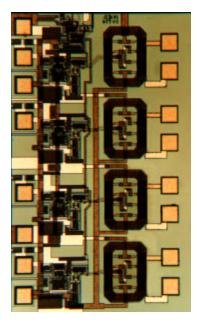

**Vertical integration** implies the capability to design isolators and their associated circuits in multiple numbers on the same piece of silicon to effect multiple channel devices. With little cost addition, four, eight or 16 channel isolated interfaces can be created. Examples of highly parallel modules are isolated IEEE 1394 bus interfaces, byte wide bus isolators, multi-channel isolated A/Ds or D/As and isolated multi-channel power switches. The extremely small footprint of the device allows high density configurations of isolated inputs and outputs whereby the packaging size is limited by pin pitch or spacing rather than by die size. The pin pitch spacing can limit dielectric breakdown voltages to the air dielectric between leads rather than any breakdown limits of the device itself. An example of vertical integration is shown in the photomicrograph of a 4 channel digital receiver (Figure 5).

**Die Photograph of Four Channel Galvanic Isolator** (1.1 x 1.9 mm)

**Figure 5: Four Channel Isolated Receiver Die**

# Conclusion

Isolation no longer needs to be thought of as a painful circuit complication only to be used in the most difficult circumstances. With the advent of a monolithic integrated isolation function, a high risk problem can be alleviated with almost no cost and space penalty.