# Address line-assisted switching of vertical magnetoresistive random access memory (VMRAM) cells

John M. Anderson and David J. Brownell NVE Corporation

Gary A. Prinz, Harold Huggins, Luan V. Van, and Joseph A. Christodoulides

Naval Research Laboratory

Jian-Gang Zhu

Carnegie-Mellon University

#### Presentation Outline

- VMRAM Overview

- VMRAM Technology

- Bits and Sense Lines

- MR Response

- Reading and Writing

- Arrays w/ Address Lines

- Test and Analysis

- IC Prototype

- VMRAM vs. Hard Disk Drive

- Conclusion

#### VMRAM Overview

- VMRAM = Vertical Magnetoresistive Random Access Memory

- Devised and developed by researchers at NRL and CMU

- NRL: Dr. Gary Prinz<sup>1,2,3</sup>, Dr. Konrad Bussmann<sup>2</sup>

- CMU: Dr. Jian-Gang Zhu¹

- VMRAM cells consist of toroid-shaped elements that have a stable closed-flux magnetic configuration

- Employs current perpendicular to the plane (CPP) to switch soft (read) and hard (write) magnetic layers of a GMR multilayer

- Address (word) lines generate radial torque fields that assist switching

- Teams from NVE Corp. and NRL have developed processes to fabricate 64-bit strings of 0.6μm O.D./0.2μm I.D. cells with address lines

- VMRAM is a high-density, non-volatile memory theoretically scaleable to 400Gbits/in<sup>2</sup> at λ = 10nm<sup>1</sup> and has the potential to compete with both semiconductor memories and mechanical hard disks.

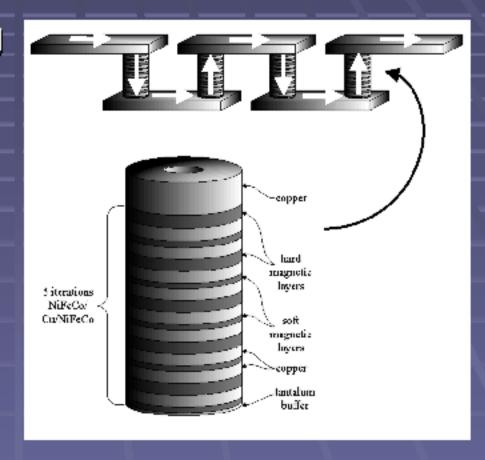

#### VMRAM Technology – Bits and Sense Lines

- 2000Å CMP'd Cu

- 40Å Ta phase breaking layer

- Multilayer stacks: [NiFeCo (20Å)/Cu (40Å)/ NiFeCo (40Å)/Cu (40Å)]x5

- 2000Å Cu connects cells such that current flows vertically

- Test arrays consist of 256 bits in 4x64-bit strings

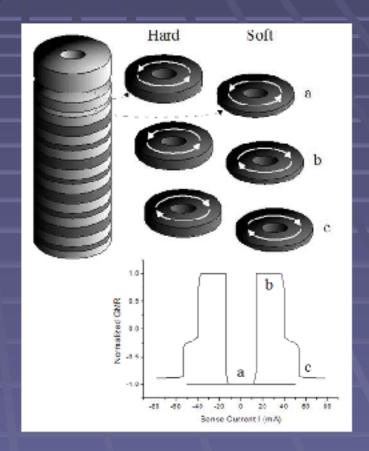

#### VMRAM Technology – MR Response

- Response shape is similar to pseudo-spin valve

- Thicker (hard) layers act as storage mechanisms

- Thinner (soft) layers act as read mechanisms

- Simulated Response

- Soft layers switch ~15mA

- Hard layers switch 40 55mA

- Address line current effectively reduces switch thresholds

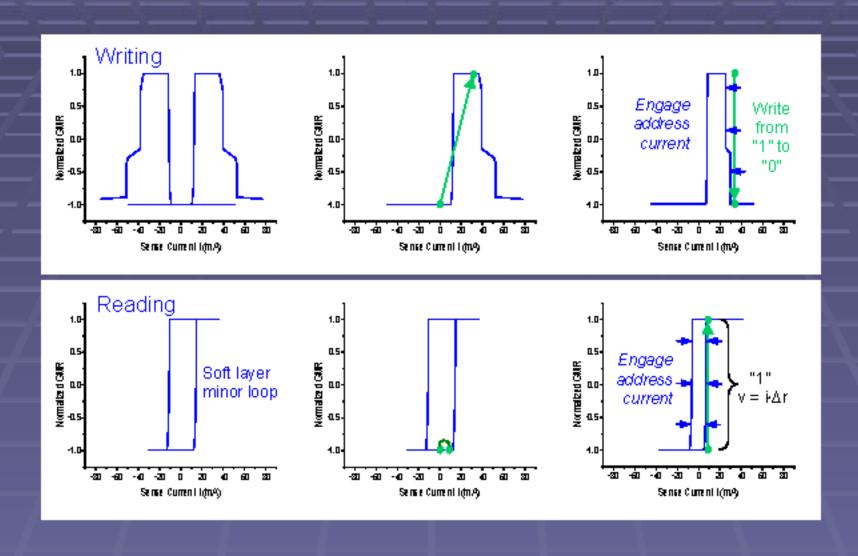

# VMRAM Technology - Writing/Reading

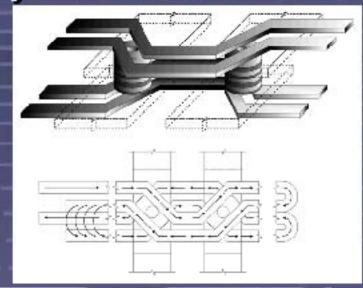

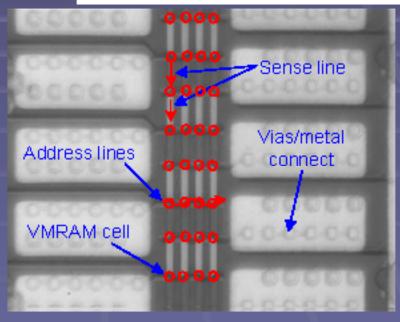

#### VMRAM Technology – Array w/ Address Lines

- Serpentine arrangement yields orthogonal upper/lower address lines

- Address current generates an outward radial word field for the current direction shown

- 4x64 arrays (4x8 section shown)

- 4 sense lines run vertically

- Address lines run horizontally

- 2-D selection

- Top and bottom address line segments connect through vias

- VMRAM cells reside at the junctions 32 cells shown

#### Test and Analysis – General Test Procedure

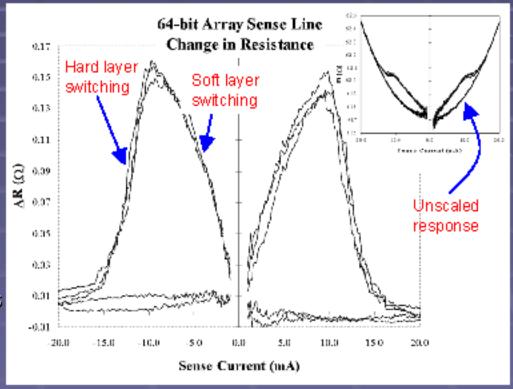

- Run bipolar sense current sweep to determine switch thresholds (+/- I<sub>th</sub>)

- Establish reference by saturating bits with +I<sub>th</sub>mA and sweeping the sense line with the same polarity current

- Saturate sense line with < |-I<sub>th</sub>mA| and I<sub>addr</sub> mA

- Sweep sense current from +I<sub>small</sub>mA to +I<sub>th</sub>mA

- Read voltage at each sense current step:

- Sample voltage

- Assert address current

- Sample voltage

- Generate MR transfer curve

- Scale data by subtracting out reference curve

### Test and Analysis – MR Response

- Observations:

- GMR <1% vs. 10%-20%</li>

- Smooth transitions for hard and soft layers vs. abrupt switching

- Suspected cause: magnetic material redeposition

- couples the stack layers

- limits antiparallel alignment between hard/soft layers

- and/or, significantly reduces the number of "active" layers

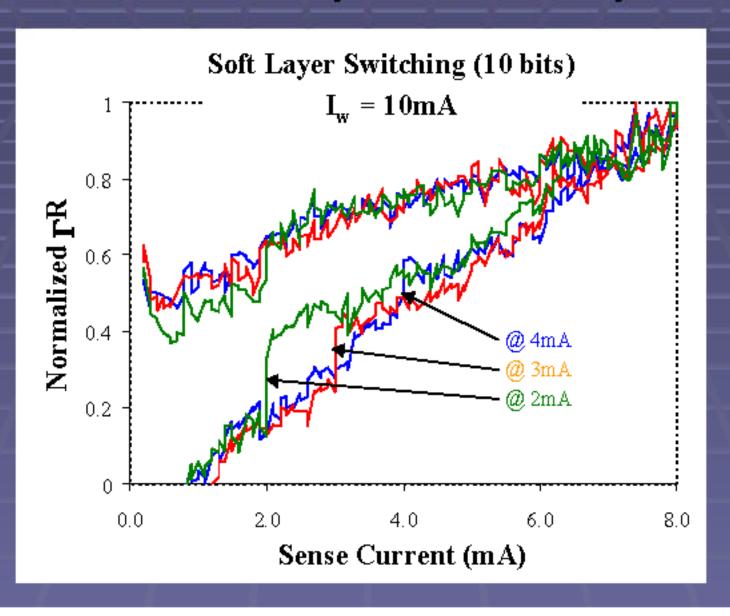

### Test and Analysis – Read Layer

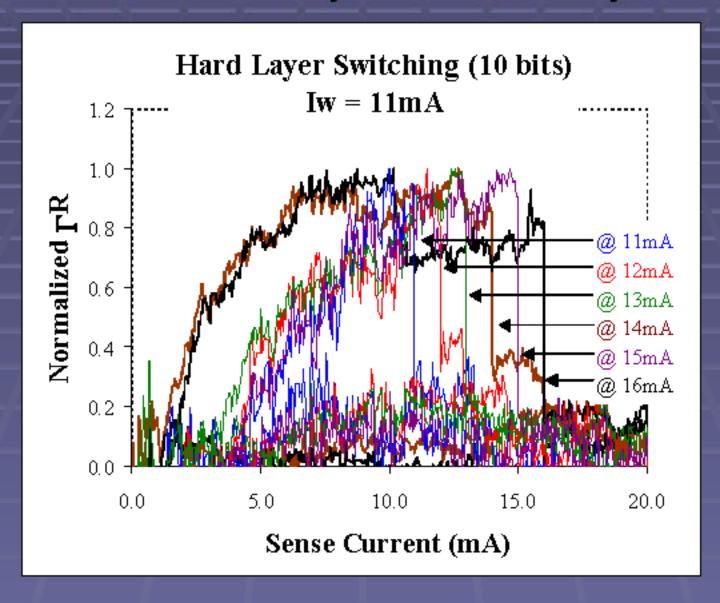

### Test and Analysis – Write Layer

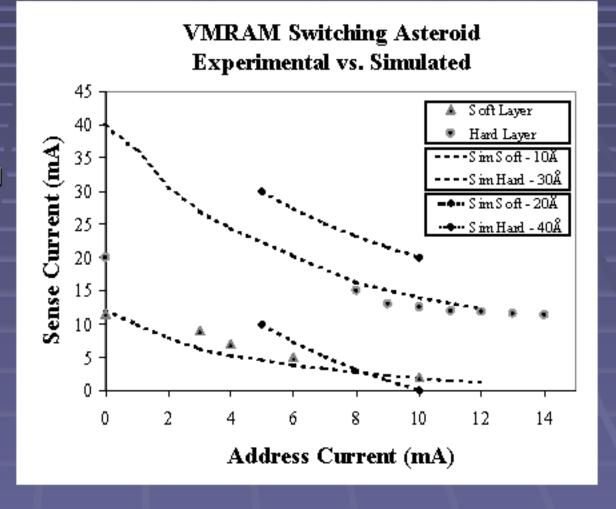

#### Test and Analysis – Switching Asteroid

- Soft layer operating point

- I<sub>sense</sub> = 6mA

I<sub>addr.</sub> = 5mA

- Hard layer operating point

- I<sub>sense</sub> = 12mA

I<sub>addr.</sub> = 10mA

- Experimental data tends toward simulated 10Å/30Å combination

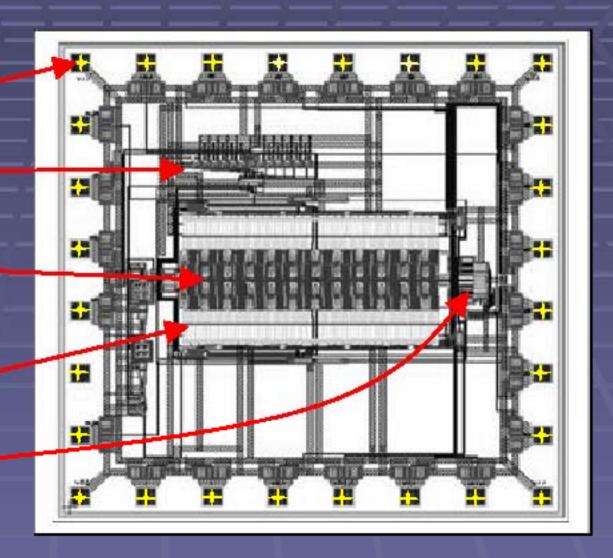

## VMRAM 2K IC Prototype Design

Bonding pads

Control logic

2 - 4x256 VMRAM arrays

Decoder circuitry

Sense amplifier

#### VMRAM vs. HDD (Projected)

- VMRAM Density at λ = 0.01μm node

- Best case: 16λ² = 403 Gbits/in²

- Worst case: 18.77λ² = 358 Gbits/in²

- VMRAM compared to a 147GB HDD\*

- $\lambda = 0.09 \mu m \text{ node}$

- 9mm x 9mm PLCC package can hold 270 305Mb

- HDD\* FF => 4" x 5.78" x 1.03"

- Same sized VMRAM memory module yields 65 75GB

- A VMRAM memory module built today could have ~50% the capacity of today's HDD

- At λ = 0.08μm (ITRS projection for 2005) capacity is ~65%

- VMRAM has no mechanical wearout

- Smaller, rugged, more versatile form factor

#### Conclusion

- Four by sixty-four bit VMRAM test arrays were successfully fabricated using address lines designed for 2-D selection.

- Address-assisted switching of VMRAM cells was demonstrated

- Soft layer switching: I<sub>sense</sub> = 6mA, I<sub>addr</sub> = 5mA

- Hard layer switching: I<sub>sense</sub> = 12mA, I<sub>addr.</sub> = 10mA

- Edge pinning in the GMR stack due to magnetic material redeposition led to low signal response and smooth transitions in unassisted MR response.

- GMR multilayer optimization is needed in order to maximize signal and ensure "singular" switching thresholds for stack magnetic layers.

- Integrated 2K VMRAM prototype design has been completed for a 0.35µm gate length semiconductor process.

- Hard and soft layer switching asteroids generated from experimental data compare well with micromagnetic simulations.

- NVE Corporation thanks the Office of Naval Research and the Naval Research Laboratory for their continued support and collaboration